瑞薩自研RISC-V CPU核心 擴充32位元MCU IP產品組合

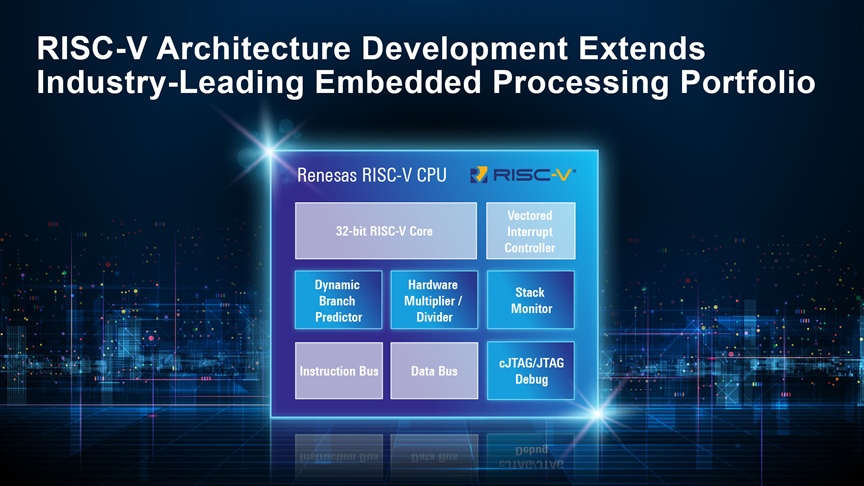

瑞薩電子(Renesas Electronics)宣布設計並測試基於開放標準RISC-V指令集架構(ISA)的32位元CPU核心。該核心由瑞薩自行開發,使其成為獨立開發RISC-V CPU核心的公司之一。

在此之前,瑞薩採用晶心科技開發的CPU核心,已推出32位元語音控制和馬達控制ASSP元件,以及RZ/Five 64位元通用微處理器(MPU);此次宣布自行研發之CPU核心,象徵該公司在新興RISC-V市場邁出下一步。新的RISC-V CPU核心將擴充瑞薩現有的32位元微控制器(MCU)IP產品組合,包括RX系列和基於Arm Cortex-M架構的RA系列。

RISC-V是開放指令集架構,首席產品行銷工程師Giancarlo Parodi表示,從頭開始打造架構讓設計人員能夠決定要將哪些元素加入處理器中,因此可以優化最終功耗、性能表現和所占面積,確保所做出的權衡(Trade-off)皆符合應用需求。採用瑞薩全新RISC-V核心的CPU適用於多種應用,可以用作主要控制器或作為SoC、晶片中子系統甚至是深度嵌入式ASSP中的輔助核心。

瑞薩RISC-V CPU的功能已實作於矽晶片進行驗證,實現3.27 CoreMark/MHz效能。瑞薩目前向特定客戶提供基於新核心的樣品,預計2024年第一季推出首款基於RISC-V的MCU及相關開發工具,產品發布後,也將可在EEMBC網站查詢進一步細節。